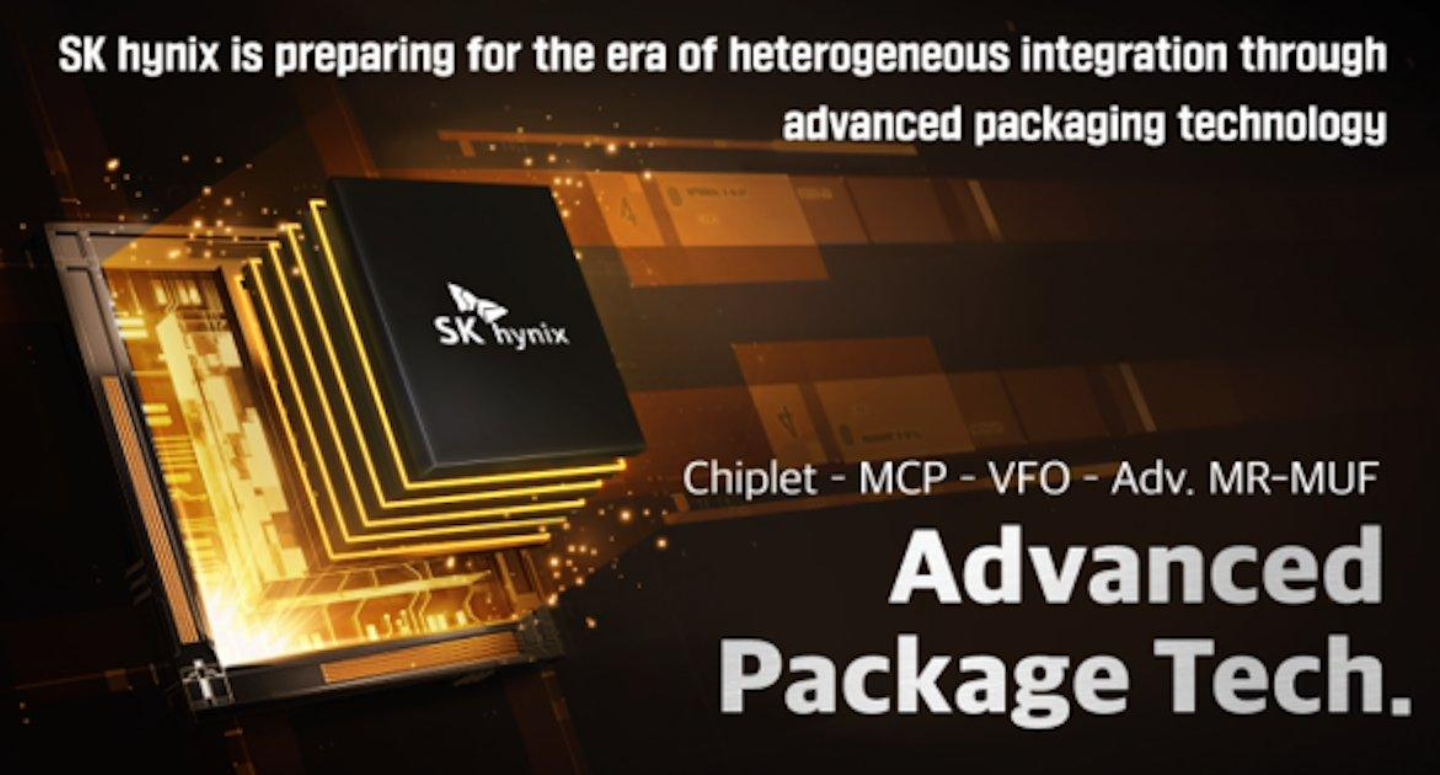

SK海力士计划将下一代HBM采用2.5D扇出封装技术

发布时间:2023-11-28 16:26:00 阅读量:1188

SK海力士正准备推出“2.5D扇出”封装,作为其下一代存储半导体技术。SK海力士今年在高带宽内存(HBM)领域取得了成功,对下一代芯片技术领域充满信心,似乎正在通过开发“专业”内存产品来确保其技术领先地位。根据韩媒 Business Korea 报道,SK 海力士正准备将 2.5D 扇出封装技术集成到其继 HBM 之后的下一代 DRAM 中。

这种封装方案是将两个 DRAM 芯片水平并排放置,然后将它们组合成一个芯片。这种方案的优势是由于芯片下方没有添加基板,可以让成品微电路更薄。SK海力士最快明年公开采用这种封装方式的研究成果。

SK 海力士的尝试非常独特,因为 2.5D 扇出封装在内存行业从未尝试过。该技术主要应用于先进系统半导体制造领域。台积电2016年首次将扇出芯片级封装(FOWLP)商业化,将其16纳米应用处理器与移动DRAM集成到iPhone 7的一个封装中,从而使这项技术推向舞台。三星电子从今年第四季开始将这一技术导入Galaxy智能手机高级AP封装中。

HBM 型存储芯片的垂直集成固然可以显著增加接口带宽,但成本高昂,而 SK 海力士研发的“2.5D fan-out”,能有效降低生产 DRAM 芯片成本,预估会在游戏显卡的 GDDR 显存中使用。

除了利用这项技术外,SK海力士也努力巩固与英伟达的合作,后者在HBM市场处于领先地位。此外,SK 海力士还为苹果新款 AR 设备“Vision Pro”中安装的“R1”计算单元生产并供应了专用 DRAM。SK 海力士总裁郭诺贞表示:“在人工智能时代,我们将把存储半导体创新,针对每个客户提供差异化的专业产品。”

相关文章阅读

-

三星、SK海力士对通用存储芯片增产持保守态度

2024-05-22

-

SK海力士再获HBM大单 客户存款大增

2024-05-21

-

SK海力士将为特斯拉生产电源管理(PMIC)芯片

2024-05-16

-

SK海力士计划2026年推出HBM4E内存 带宽为上代1.4倍

2024-05-14

-

三星、SK海力士将停供DDR3 或致价格飙涨

2024-05-13

-

SK海力士开发新一代移动端NAND闪存解决方案

2024-05-10

-

SK海力士表示2025年生产的HBM产品基本售罄

2024-05-06

-

SK海力士考虑新建DRAM工厂应对需求增长

2024-04-29

热门分类

推荐产品

资讯排行榜

关注我们