台积电预计2030年实现1纳米制程芯片生产

发布时间:2023-12-29 11:00:00 阅读量:1413

台积电日前在2023年IEEE国际电子元件会议(IEDM)上,发布进军至1nm制程的产品规划蓝图,这一计划与英特尔去年透露的规划类似。

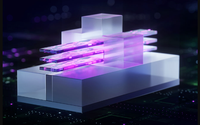

根据规划,台积电将并行推动3D封装和单芯片封装的技术路径的发展。预计在2025年,台积电将完成N2和N2P节点,使得采用3D封装的芯片晶体管数量超过5000亿个,而采用传统封装技术的芯片晶体管数量超过1000亿个。

_20231229112446_662.jpg)

台积电计划在2027年达到A14节点,并在2030年达到A10节点,即1nm制程芯片。届时,采用台积电3D封装技术的芯片晶体管数量将超过1万亿个,而采用传统封装技术的芯片晶体管数量将超过2000亿个。

据悉,台积电将使用EUV极紫外光刻、新通道材料、金属氧化物ESL、自对齐线弹性空间、低损伤低硬化低K铜材料填充等等一系列新材料、新技术,并结合CoWoS、InFO、SoIC等一系列封装技术。

台积电在会议上还透露,其 1.4nm 级工艺制程研发已经全面展开。同时,台积电重申,2nm 级制程将按计划于 2025 年开始量产。

尽管台积电的发展速度有所放缓,但其在半导体代工领域的竞争对手,如三星等公司,仍在不断努力追赶台积电在先进制程领域的领先地位。今年六月,三星代工公布了其最新的工艺技术发展路线图,计划在2025年推出2纳米制程的SF2工艺,并在2027年推出1.4纳米制程的SF1.4工艺。如果这些计划能够如期实现,三星有可能在与台积电相似的时间节点上实现类似的先进工艺水平。

相关文章阅读

-

台积电预测AI加速器市场或将增长250%

2024-05-27

-

市场需求强劲 台积电计划2024年新建七座工厂

2024-05-24

-

苹果高管访问台积电 或将包下2nm产能

2024-05-23

-

ASML声称可远程瘫痪台积电光刻机引发关注

2024-05-22

-

台积电推出N4e制程 特殊制程产能提升50%

2024-05-21

-

台积电CoWoS产能仍供不应求

2024-05-20

-

台积电3nm工艺步入正轨 2024下半年将如期投产N3P节点

2024-05-17

-

台积电拟四季度开建欧洲工厂 预计2027年投产

2024-05-15

热门分类

推荐产品

资讯排行榜

关注我们