台积电与力晶携手推出3D整合芯片 已开始量产并出货

发布时间:2021-08-27 14:50:07 阅读量:1676

台积电、力晶两大集团携手,透过DRAM与逻辑芯片的真3D堆叠异质整合技术,打造全球最强异质整合芯片,协助客户打破摩尔定律的限制,领先英特尔、三星等劲敌,为全球首创。该3D整合芯片提供相对于现有高带宽存储器(HBM)十倍以上的高速带宽及数倍容量,为中国台湾地区半导体业筑起更难超越的高墙。

力晶集团昨(25)日透过旗下客制化产品研发暨智财授权商爱普,宣布这项讯息。这是中国台湾地区半导体技术又一大突破,相关产品已开始量产出货,锁定区块链、AI、网通等先进应用,过程当中,爱普“小兵立大功”,负责引案、设计、研发等工作,并串连台积电在逻辑芯片代工与3D堆迭制造能力,以及力晶旗下力积电存储器代工制造能量,打造出世界第一的异质整合晶片。

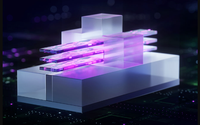

此次两大集团合作分工,由爱普提供的VHM(3D堆叠技术存储器),包含客制化DRAM设计及DRAM与逻辑芯片整合介面的VHM LIn KIP;力积电供应客制化DRAM晶圆代工制造,最后由台积电提供逻辑制程晶圆代工及3D堆叠制造服务。

台积电自十年前开始耕耘先进封装,陆续开发CoWoS、封装内封装乃至逐步发展自先进封装3D fabric整合平台,在今年技术论坛上也特别说明先进封装产能扩充计划。

力积电表示,逻辑芯片与DRAM的3D整合,是力积电在AI存储器策略上的最新成果,这项3D技术将可为DRAM的带宽创造前所未见的可能性,对于AI、网通及图像处理等特别需要大量带宽的应用,将有极大的帮助。

爱普表示,半导体封装技术已从传统的2D封装演进到2.5D,再到真正的3D封装,而2.5D封装是将多片芯片封装于同一块硅中介板上,但真正的3D封装技术则是以垂直的连接方式,将多片芯片直接立体地互相堆叠,相较于2.5D封装,逻辑芯片与DRAM的3D整合,将可在显著降低传输功耗的同时,同时大幅提升内存的带宽。

此次推出的3D整合芯片,提供相对高带宽存储器十倍以上的高速带宽,搭载超过4GB内存容量,并且是7纳米制程逻辑芯片内存SRAM最大容量的五到十倍。

标签: 力积电 台积电

郑重声明:本文版权归原作者所有,转载文章仅为传播更多信息之目的,如作者信息标记有误,请第一时间联系我们修改或删除,感谢您的关注!