远远不及预期 外媒报道三星3nm良率仅10%-20%

发布时间:2022-04-19 13:04:10 阅读量:1262

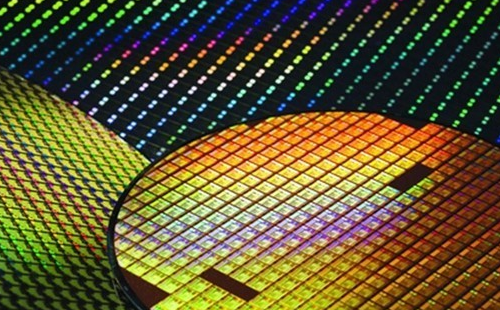

继台积电宣布今年下半年将开启3nm芯片量产之后,三星3nm制程芯片已经开始试产。韩国媒体的报道显示,三星电子3nm制程工艺的良品率,才到10%-20%,远不及公司期望的目标,在提升3nm工艺的良品率方面,也陷入了挣扎。

三星电子和台积电是目前已顺利量产5nm工艺,并在推进3nm工艺量产事宜的晶圆代工商,与台积电继续采用鳍式场效应晶体管(FinFET)架构不同,三星电子3nm工艺采用的是全环绕栅极晶体管(GAA)技术。据Digitimes,三星基于GAA晶体管的3nm工艺良率远低于预期,这或许意味着公司需要更多的时间才能投入量产。所谓GAA晶体管即环绕栅极晶体管,它取代的是FinFET(鳍式场效应晶体管),前者可以实现四边充当电流通道,二者则只有三边。

三星本来想着通过抢占技术制高点“降维”打击台积电,没想到后者坚持在3nm使用FinFET后,结果更务实。今年早些时候曾有报道称,半导体设备巨头Lam Research(泛林)向三星提供了用于3nm GAA芯片蚀刻相关的机器,三星希望在上半年完成全套工艺的质量验证。

值得注意的是,在今年2月份曾有报道称,三星重要客户高通明年将推出的3nm工艺应用处理器,将交由台积电代工,同时由于4nm工艺的良品率低,高通也已将部分骁龙8 Gen 1交由台积电代工,不再由三星电子独家代工。台积电和三星很快就会有新的挑战者,因为英特尔曾表示,其目标是在 2024 年底之前接管行业的制程领导地位。它还率先获得了更先进的极紫外 (EUV) 光刻机。

第二代 EUV 机器被称为High NA 或高数值孔径。当前的 EUV 机器的 NA 为 0.33,但新机器的 NA 为 0.55。NA 越高,蚀刻在晶圆上的电路图案的分辨率就越高。这将帮助芯片设计人员和代工厂制造出新的芯片组,其中包含的晶体管数量甚至超过了当前集成电路上使用的数十亿个晶体管。

它还将阻止代工厂再次通过 EUV 机器运行晶圆以向芯片添加额外的功能。ASML 表示,第二代 EUV 机器产生的更高分辨率图案将提供更高的分辨率将使芯片特征小 1.7 倍,芯片密度增加 2.9 倍。

通过首先获得这台机器,英特尔将能够朝着从台积电和三星手中夺回制程领导地位的目标迈出一大步。

标签: 三星

郑重声明:本文版权归原作者所有,转载文章仅为传播更多信息之目的,如作者信息标记有误,请第一时间联系我们修改或删除,感谢您的关注!